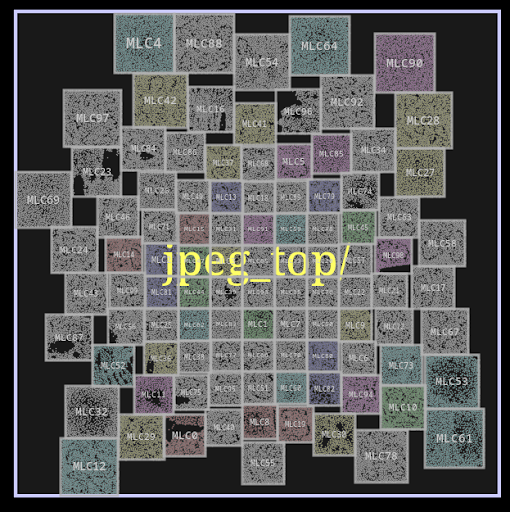

The SiHi VLSI Partitioner provides the unique capability to seamlessly divide and conquer large gate-level netlists to a preset number of physical design partitions. These partitions may be extracted as a multi-level hierarchical netlist and be used for Block based design. It plays a crucial role in the design flow of complex integrated circuits, helping designers manage design complexity, optimize performance, and achieve faster time-to-market for semiconductor products.

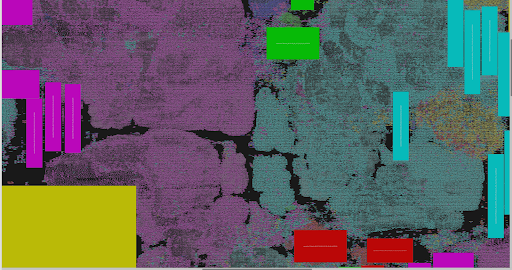

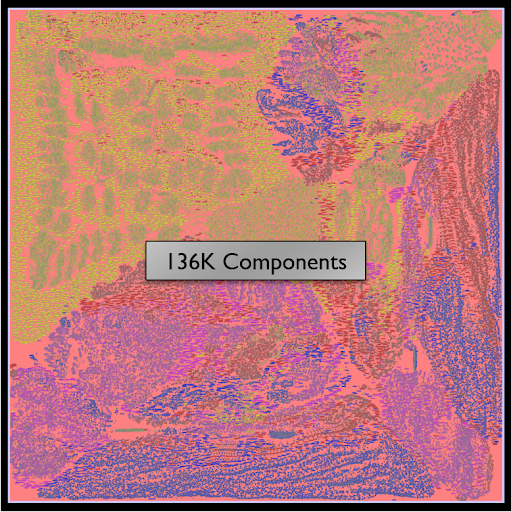

The SiHi VLSI Partitioner takes a gate-level netlist as input and generates a new gate-level netlist as output representing the partitioned design. It considers gate-level standard cell connectivity and area, as well as timing information, i.e. slack, (if provided) to generate loosely dependent partitions, generated as Verilog physical hierarchy modules. The number of partitions and key partitioning parameters are highly flexible and tunable by the users. The resultant, partitioned physical hierarchy netlist exposes a new, modular hierarchy with optimized connectivity, making the partitioned design suitable for further Block based processing EDA flow steps, including physical design, verification, or synthesis.

Copyright © 2023 Silicon Highway (SiHi) Technologies, All rights reserved. Designed & Created by Onum Group