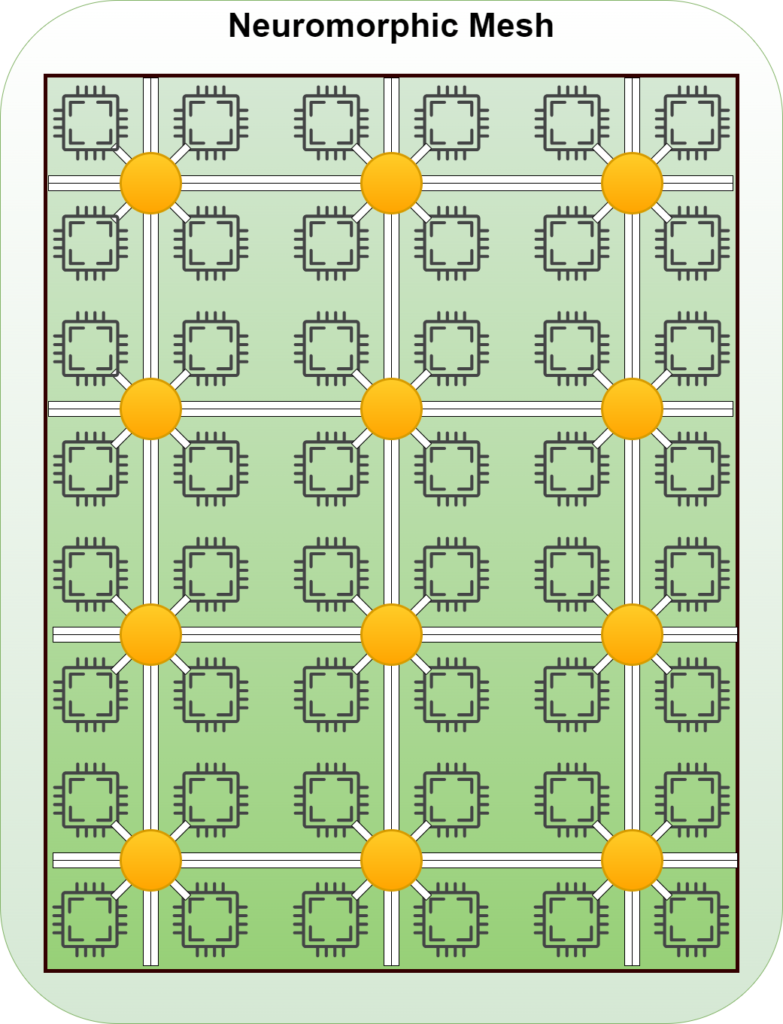

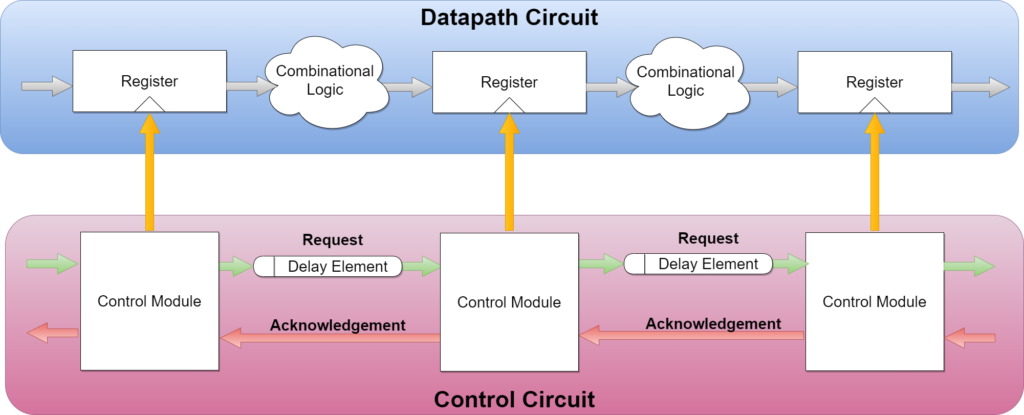

This is the world’s premier Asynchronous Static Timing Analysis (ASTA) tool, capable of performing Static Timing Analysis on Fully-Asynchronous, Bundled-Data circuits, Mixed Synchronous, Asynchronous, or cyclic digital circuits. SiHi’s ASTA tool can handle circuits with an arbitrary number of combinational cycles, asynchronous circuits, with an explicitly specified environment and closed loop cyclic circuits. ASTA is essential for verifying the timing behavior of designs, where synchronous and asynchronous portions coexist within the same system, or cyclic circuits, such as Ring Oscillators, Voltage to Time Converters (VTCs), Globally Asynchronous Locally Synchronous Networks-on-Chips (GALS NoCs) modules, and Neuromorphic NOC circuits.

The ASTA tool plays a crucial role in verifying the timing behavior of Fully-Asynchronous, Bundled-Data circuits, Mixed Synchronous, Asynchronous, or cyclic digital circuits, ensuring that they meet performance requirements and operate correctly under all possible operating FEOL and BEOL conditions. It assists designers to identify and address timing issues early in the design cycle, leading to improved design quality and reduced time-to-market for high-quality electronic products. It can automatically detect timing critical portions of the circuit, report and optimize circuit performance. The tool supports industrial formats such as SDF, SAIF, SPEF, SDC, etc., as well as has a flexible interface to other EDA tools for seamless integration into complex EDA flows.

Copyright © 2023 Silicon Highway (SiHi) Technologies, All rights reserved. Designed & Created by Onum Group